Parasitic capacitance is virtual capacitance (usually unnecessary) between two conductive structures separated by an insulator. It is an effect in PCB layout, where the propagating signal behaves as if it is a capacitor, but it is not a real capacitor. Parasitic capacitance usually occurs between any pair of conductors separated by a dielectric.

These capacitances are not intentionally designed, but are caused by factors such as circuit layout, distance between conductors, and insulating materials. When designing circuits, the effects of parasitic capacitance are usually considered and minimized as they may cause changes or interference in circuit performance.

Parasitic capacitance mainly comes from the following aspects:

Capacitance between components, such as capacitance generated by wires and pins between different components.

Capacitance between components and ground, such as capacitance generated by wires and pins between components and ground.

Capacitance on PCB boards, such as capacitance formed between different wires and between wires and ground.

Capacitance generated by other factors, such as electromagnetic interference, temperature changes, etc.

Effects of parasitic capacitance on circuits:

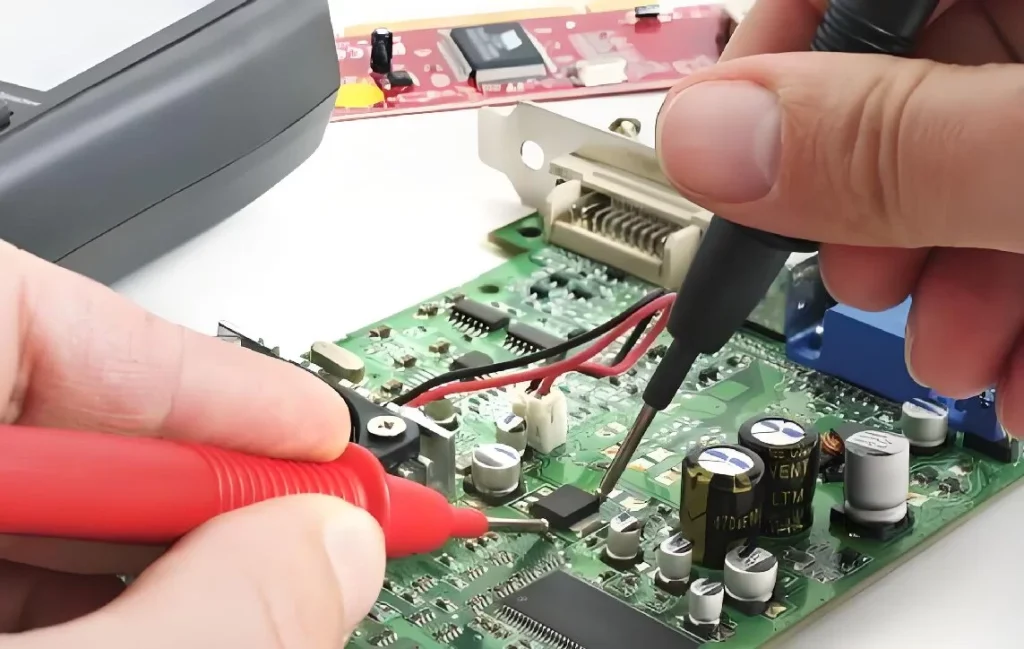

Parasitic capacitance is ubiquitous, hidden, and cannot be measured by instruments. Therefore, the influence of parasitic capacitance is very difficult to analyze, which brings great challenges to the analysis and debugging of EMC problems.

- Changes the signal return path

The high-frequency current loop area is an important factor affecting radiation emission, and the controllable current loop area is an important prerequisite for ensuring EMC performance. The existence of parasitic capacitance will change the return path of high-frequency current, and its loop area will also increase accordingly, causing serious EMC problems.

- Capacitive coupling crosstalk

In the process of EMC problem analysis and debugging of switching power supply, it is found that capacitive coupling is an important reason for the failure of power supply end conducted disturbance test. Capacitive coupling often occurs between two wirings with a large potential difference. Capacitive coupling will reduce the performance of the filter, or even bypass it and fail.

- Generates parasitic oscillation

Parasitic oscillation often occurs between the parasitic capacitance between the pins of power devices such as diodes, MOS tubes, semiconductor chips, and the parasitic inductance of inductors, transformers, magnetic beads, and PCB Layout wiring in the line. Parasitic oscillation in switching power supply products is one of the important reasons for EMI test failure, but it is easily overlooked by design engineers.

In the process of EMC problem analysis and debugging of switching power supply, it is found that capacitive coupling is an important reason for the failure of conducted disturbance test at the power supply end. Capacitive coupling often occurs between two wirings with a large potential difference. Capacitive coupling will reduce the performance of the filter, or even bypass it and fail.

- Produces dipole antenna

Metal conductors are often used for electromagnetic interference shielding. Good overlap design between metal conductors is the prerequisite for ensuring high-quality shielding effect. In actual structural design, the oxidation problem of metal conductors is taken into consideration, and insulating paint is sprayed on the metal surface to avoid metal oxidation. When two metals sprayed with insulating paint are overlapped together, they cannot be well conducted to form an equipotential body. When high-frequency noise current flows through one of the conductors, an induced electromotive force will be generated on the other conductor to form an electric dipole antenna, radiating the noise.

Methods to reduce parasitic capacitance:

Reduce the distance between conductors: The size of parasitic capacitance is inversely proportional to the distance between conductors, so the value of parasitic capacitance can be reduced by reducing the distance between conductors. This includes minimizing the length of wires in circuit board design and keeping the distance between wires as small as possible when laying out wires.

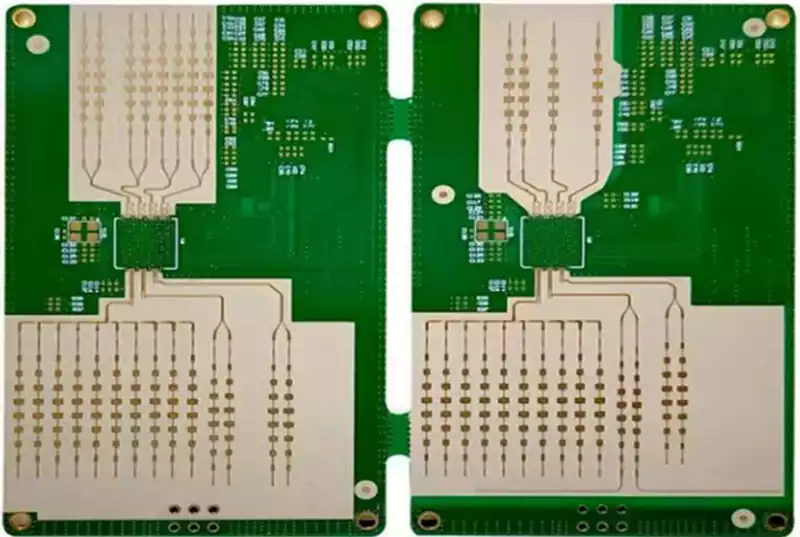

Optimize interlayer structure: In multi-layer circuit board design, reasonably plan the stacking order and copper plating method between layers to minimize the parasitic capacitance between layers.

Use shielding structure: In high-frequency circuit design, shielding structure can be used to isolate electromagnetic coupling between different signal lines or signals and ground lines, thereby reducing the influence of parasitic capacitance.

Choose suitable materials: Select materials with low dielectric constant and low dielectric loss as the base material and insulating material of the circuit board to reduce the size of parasitic capacitance.

Use differential signal transmission: In high-speed signal transmission, using differential signal transmission can effectively reduce the influence of parasitic capacitance and improve the anti-interference ability of the signal.

Ground wire design: Reasonably design the ground wire, minimize the area and length of the ground wire loop, and reduce the capacitive coupling between the ground wire and the signal line.

In summary, understanding the negative impact of parasitic capacitance and improving it can effectively reduce the influence of parasitic capacitance and improve the performance and stability of the circuit. This is My Sharing.