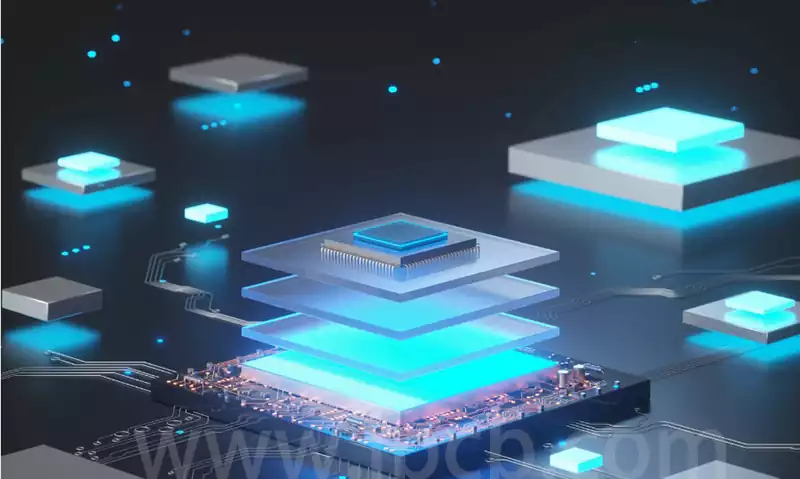

Hybrid bonding is an emerging packaging technology that combines the features of inter-chip bonding and intra-chip bonding. It utilises different bonding techniques to achieve interconnections between wafers and package substrates or within wafers to meet the needs of high-performance integrated circuits with complex interconnect structures.

There are two common types of hybrid bonding:

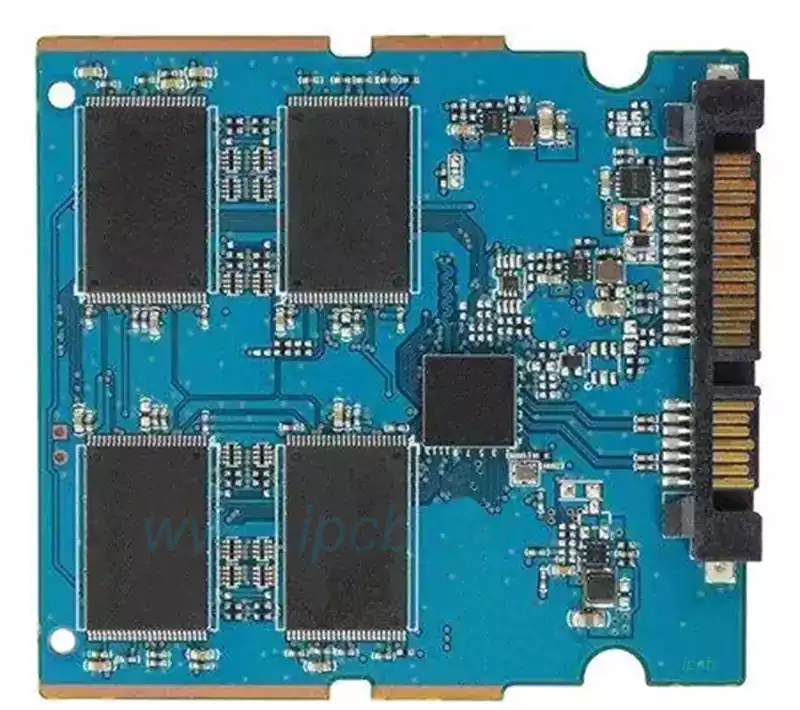

- Wafer to Wafer (W2W) wafer-to-wafer: suitable for high yield chips, such as CMOS, 3D NAND. 2. Die to Wafer (D2W) chip-to-wafer: suitable for different types of chip integration, such as heterogeneous integration.

W2W can provide higher alignment accuracy, throughput and bonding yield. However, a major limitation is the inability to select a known qualified die (KGD). This can result in bonding defective chips to good ones, leading to wastage of good quality chips.Another disadvantage of W2W is that the dimensions of the chips on the two wafers have to be the same, thus limiting the flexibility of the heterogeneous integration option. Therefore, W2W is suitable for wafers with high yields, usually designed for smaller chip sizes, such as CMOS image sensors and 3D NAND.

D2W allows selective integration of chips of different sizes and process nodes (e.g., logic chips and memory chips) onto the same wafer, thus supporting heterogeneous integration and customised design, and avoiding the yield loss problem caused by whole wafer bonding in W2W (e.g., when there are defects in one wafer, only a single chip is affected, not the whole wafer). In addition, D2W can be bonded by screening the qualified chip (KGD) through step-by-step testing, reducing overall costs. This feature makes it more adaptable in advanced packages such as 3D stacking, especially for high-performance computing scenarios that require the integration of chips from multiple sources. However, the technical realisation of D2W hybrid bonding is more difficult, mainly due to the two challenges of sub-micron alignment accuracy and interface coplanarity control.

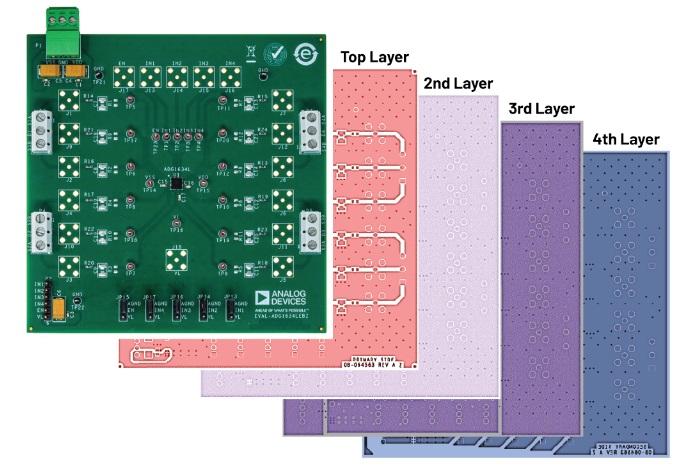

Process Flow:

Hybrid bonding technology combines both dielectric bonding and metallic interconnections, typically utilising a dielectric material (e.g. SiO₂) in combination with embedded copper (Cu) pads, to achieve a permanent electrical connection between two wafers or chips through the formation of a dielectric bond and a metallic bond without the use of solder bumps. This bump-free connection reduces signal loss and optimises thermal management, thus improving overall electrical performance.

The wafer surface is chemically and mechanically polished (CMP) to achieve a very high degree of flatness, typically requiring a surface roughness (Ra) of less than 0.5nm for SiO₂ and 1nm for copper pads. This is followed by a surface activation treatment using plasma (e.g. Ar, N₂, O₂) to enhance the hydroxyl density and hydrophilicity of the SiO₂ surface, and a reducing plasma (e.g. H₂) to remove the oxide layer on the Cu surface, to ensure that the surfaces are clean and active. Precise alignment of wafers or chips in a clean room environment ensures that the metal pads correspond perfectly to each other, avoiding bonding defects caused by particle contamination. After alignment, initial dielectric bonds are formed and the wafers are lightly bonded by van der Waals forces. Subsequently, strong bonds are achieved by atomic diffusion and mechanical interlocking at room temperature or slightly higher, under certain pressure and in an inert atmosphere. Finally, heat treatment is used to promote the diffusion of copper and dielectric layers, which further enhances the bond strength and stability of the electrical connection.

Hybrid bonding technology highlights:

Hybrid bonding is expected to play a key role in the development of packaging technology as the semiconductor industry moves towards more complex integrated systems. Innovations in materials and processes are likely to enhance its viability, making it a key enabler for next-generation devices.

Surface flatness requirements: Clean, flat contact surfaces are essential for effective bonding. Achieving this requires precise chemical mechanical polishing (CMP).

Particle Contamination: Particles on the wafer surface can compromise the integrity of the bond, leading to poor or faulty electrical connections.

Mechanical Stress Issues: The process can lead to chip cracks and wafer warpage, which can complicate alignment and bonding results.

Reduced connection reliability: As bonding technology evolves and bump heights and surface areas become smaller, it becomes increasingly challenging to make reliable electrical connections.

Cost and Complexity: The complex equipment and process controls required for hybrid bonding can lead to higher production costs, preventing widespread adoption.

Advantages of hybrid bonding technology include

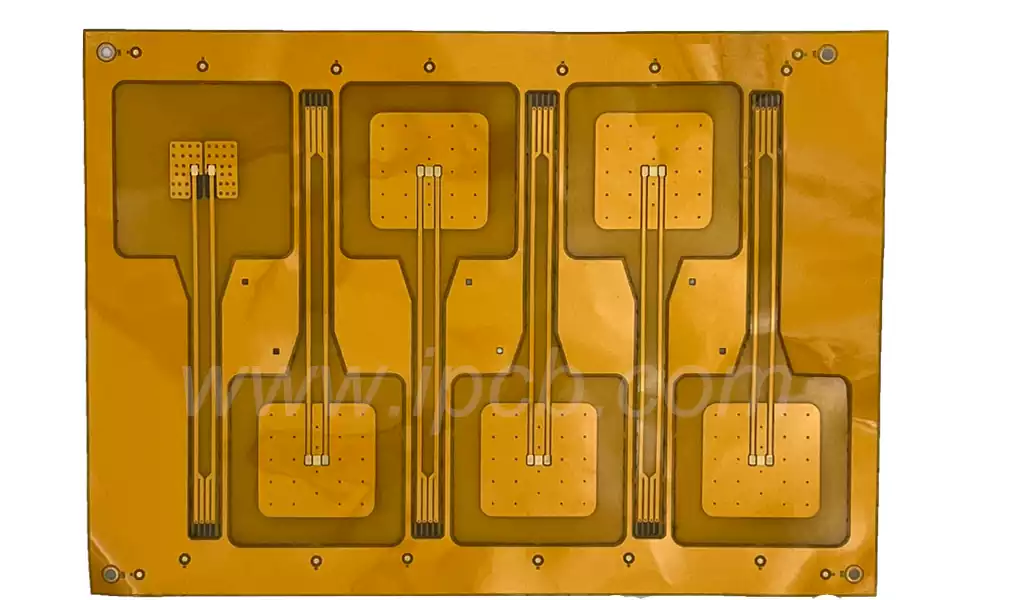

- Extremely high density interconnect: Compared to traditional bonding technology, hybrid bonding can achieve sub-micron and even nanometre interconnect spacing, allowing more connections to be placed in a smaller area, greatly increasing the bandwidth of data communication between chips.

- Low resistance, low latency: Due to the elimination of intermediate media such as solder and other materials, the direct copper-to-copper connection has a lower resistance, reducing the energy loss of signal transmission and also reducing the time delay of signal propagation.

- Better thermal performance: Compact structure and direct conductive path helps to improve thermal management and reduce heating problems, especially important for high-performance computing, artificial intelligence and other high-speed computing applications.

- Miniaturisation and high-performance packaging: Hybrid bonding technology promotes the development of 2.5D and 3D packaging, enabling chips to be integrated in a vertically stacked manner, significantly reducing the size of the final product and improving overall system performance.

Application areas of hybrid bonding technology

Hybrid bonding technology has a wide range of application prospects in the field of microelectronics packaging, mainly including the following aspects:

Three-dimensional packaging: with the development of three-dimensional integration technology, hybrid bonding technology in the realization of chip stacking, interconnection and heat dissipation has a unique advantage, and is expected to become one of the mainstream technologies of the future three-dimensional packaging.

Sensor packaging: As an important part of modern electronic equipment, the packaging performance of the sensor directly affects the stability and reliability of the sensor. The technology can achieve high-strength connection between the sensor chip and the substrate to improve the performance of the sensor.

Optoelectronic packaging: in the field of optical communications, optoelectronic devices, hybrid bonding technology can achieve efficient coupling and encapsulation of optical components and electronic components, which is conducive to improving the overall performance of optoelectronic devices.

Biomedical device encapsulation: hybrid bonding technology has a wide range of applications in biomedical device encapsulation, such as biochips, microfluidic chips and so on. It can realise the solid connection between biological materials and metals, ceramics and other materials to ensure the long-term stable work of biomedical devices.

Aerospace field: Aerospace field has very high requirements on the performance and reliability of electronic devices. Hybrid bonding technology, with its excellent mechanical properties, thermal stability and environmental adaptability, has a broad application prospect in this field.

Hybrid bonding technology, as an emerging packaging solution integrating dielectric bonding and metal interconnect, is gradually becoming the core technology of advanced microelectronics packaging by virtue of its high-density interconnect, low resistance and low latency, and excellent thermal management capabilities. Whether in three-dimensional packaging, sensor packaging, or optoelectronics, biomedical and aerospace fields, hybrid bonding has shown broad application prospects and strong technical advantages.

With the continuous progress of semiconductor process and integration continues to improve, hybrid bonding technology will further promote the chip miniaturisation, high performance development trend. In the future, through the continuous optimisation of the process and the improvement of alignment accuracy, hybrid bonding is expected to achieve higher yields and lower costs, and help the innovative design of heterogeneous integration and multifunctional systems.