TGV (Through Glass Via) technology evolved from 2.5D/3D integrated TSV interposer technology. Since its inception in 2008, it has focused on overcoming the dielectric loss bottleneck in high-frequency, high-speed signal transmission inherent to traditional silicon substrates, while addressing industry pain points such as the high cost and complex manufacturing processes associated with silicon materials. This technology centres on two core processes: glass through-hole etching and metallised interconnections. By establishing vertical interconnect channels on glass substrates, it offers a novel pathway for three-dimensional integration, positioning itself as a potential disruptive alternative to silicon substrates.

TGV Through Glass Via Process Steps

- Pre-treatment

Pre-treatment of glass substrates is a critical step in ensuring subsequent process quality, primarily involving thorough cleaning and efficient drying. First, ultrasonic cleaning utilises a combination of deionised water and organic solvents such as acetone and alcohol to effectively remove various contaminants from the substrate surface, including dust, oil residues, and organic deposits. This provides a clean starting surface for subsequent precision processing.

Following cleaning, immediate drying is essential to eliminate residual moisture from the substrate surface. This is typically achieved through two methods: either purging with high-purity nitrogen gas to rapidly remove droplets, or high-temperature baking to evaporate moisture via heat. These drying measures prevent any residual moisture from adversely affecting subsequent processing, thereby safeguarding production quality.

- Via Formation

The photolithography process begins by uniformly coating the substrate surface with photoresist. Subsequently, photolithography equipment precisely projects the predefined via pattern onto this photoresist layer. During exposure, photochemical reactions occur in the exposed areas of the photoresist. Following development with a developer solution, the unexposed photoresist is dissolved and removed, ultimately leaving a photoresist pattern that perfectly matches the via design. This patterned layer serves as a critical protective mask during subsequent etching steps, ensuring material removal occurs only in specific designated areas.

Etching Process

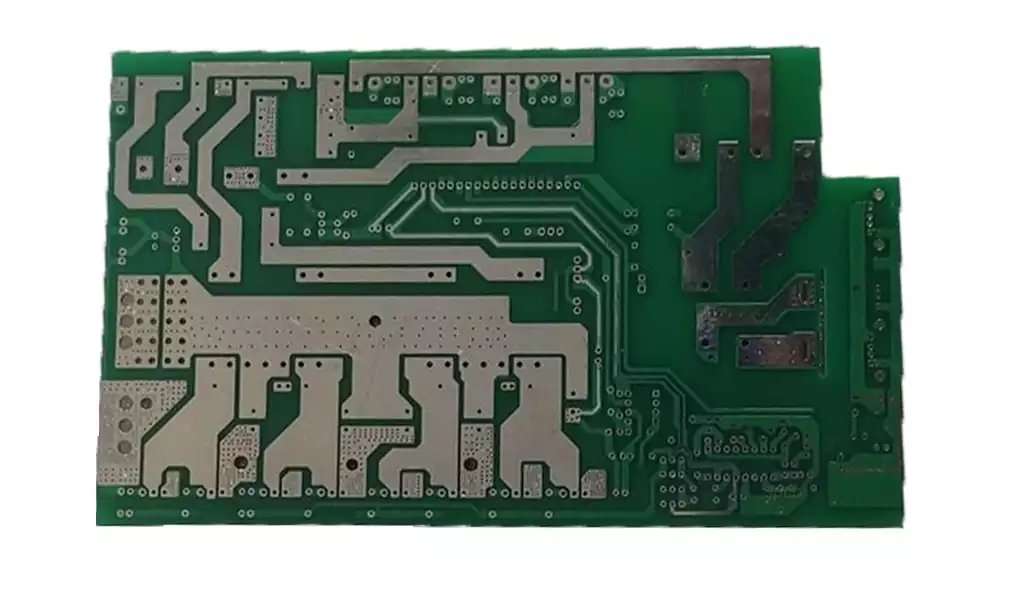

Etching constitutes a pivotal step in semiconductor manufacturing, transferring the pattern from the mask onto the material layer. Etching processes are primarily categorised into dry etching and wet etching.

Dry Etching

Dry etching typically employs Reactive Ion Etching (RIE) technology. This method utilises reactive particles generated within a plasma to chemically react with the glass material. Combined with physical bombardment, it removes glass material precisely along the photoresist mask’s contours, thereby forming the required through-hole.

Wet Etching

Wet etching involves immersing the glass substrate in an etchant solution containing corrosive liquids such as hydrofluoric acid. Through chemical dissolution, glass material is selectively removed to ultimately form the via structure.

Process Parameter Control

Whether employing dry or wet etching, stringent control of all process parameters is essential to ensure the dimensional accuracy and geometric integrity of the through-holes meet design specifications. These critical parameters include, but are not limited to, etching duration, temperature, and etchant concentration. Precise management of these factors is paramount for achieving high-quality etching outcomes.

- Through-Hole Cleaning and Surface Treatment

Cleaning: Removal of residual etchant, photoresist, and other substances from the etching process. Photoresist is stripped using specific solvents, followed by multiple rinses with deionised water to ensure cleanliness within the via and on the glass substrate surface. Surface Activation: Treatment of the glass surface and via walls with chemical solutions (e.g., those containing silane coupling agents) to enhance adhesion between the subsequent metallisation layer and the glass substrate. - Metallisation

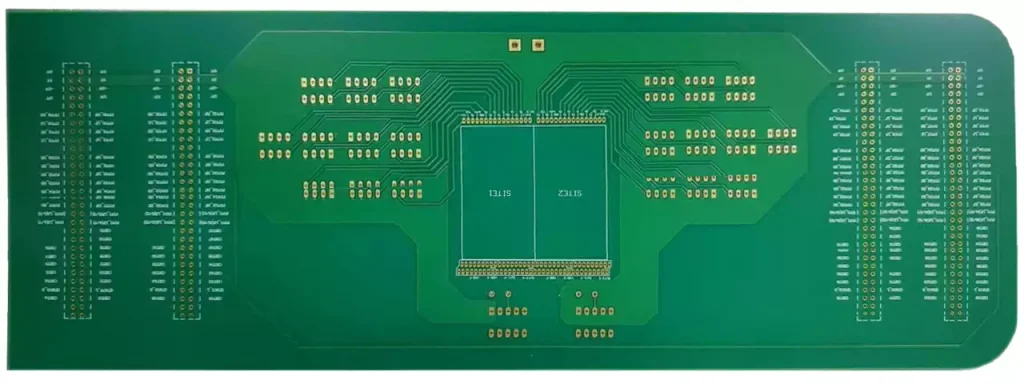

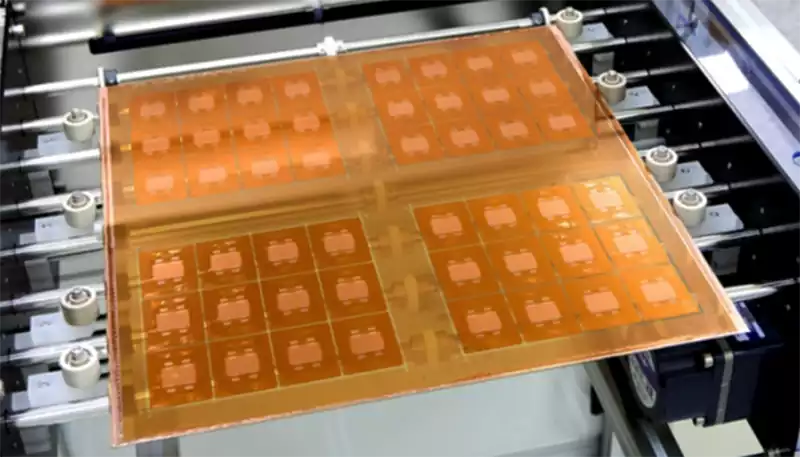

Seed Layer Deposition: Employing physical vapour deposition (PVD) sputtering or chemical vapour deposition (CVD) techniques, metals such as copper or titanium are uniformly deposited onto the glass substrate surface and via walls to form an ultra-thin metallic seed layer. This seed layer not only enhances adhesion between the substrate and subsequent fill metals but, crucially, serves as an electroplating conductive base, establishing essential current pathways for subsequent metal filling. Electroplating: Using the seed layer as an electrode, the glass substrate is immersed in an electroplating solution containing metal ions such as copper. Driven by electrical current, metal ions continuously deposit and grow within the vias and on the substrate surface until the vias are completely filled, forming dense metal interconnect pillars. Throughout this process, precise control of parameters such as current density, plating duration, and solution temperature is critical. Only through strict management of these parameters can uniform metal filling without voids be ensured, achieving high-quality electrical interconnect performance. - Planarisation and Post-Processing

Planarisation: Excess metal on the glass substrate surface is removed via processes such as chemical mechanical planarisation (CMP), ensuring surface flatness to guarantee planarity and electrical performance during subsequent interconnections with other components.

Inspection and Testing: Optical microscopes and scanning electron microscopes (SEM) are employed to examine via dimensions, morphology, and surface quality. Electrical parameters such as via resistance and capacitance are measured using electrical test equipment to verify TGV structure compliance with design specifications.

Compared to through-silicon vias (TSVs), the advantages of through glass via (TGV) primarily lie in:

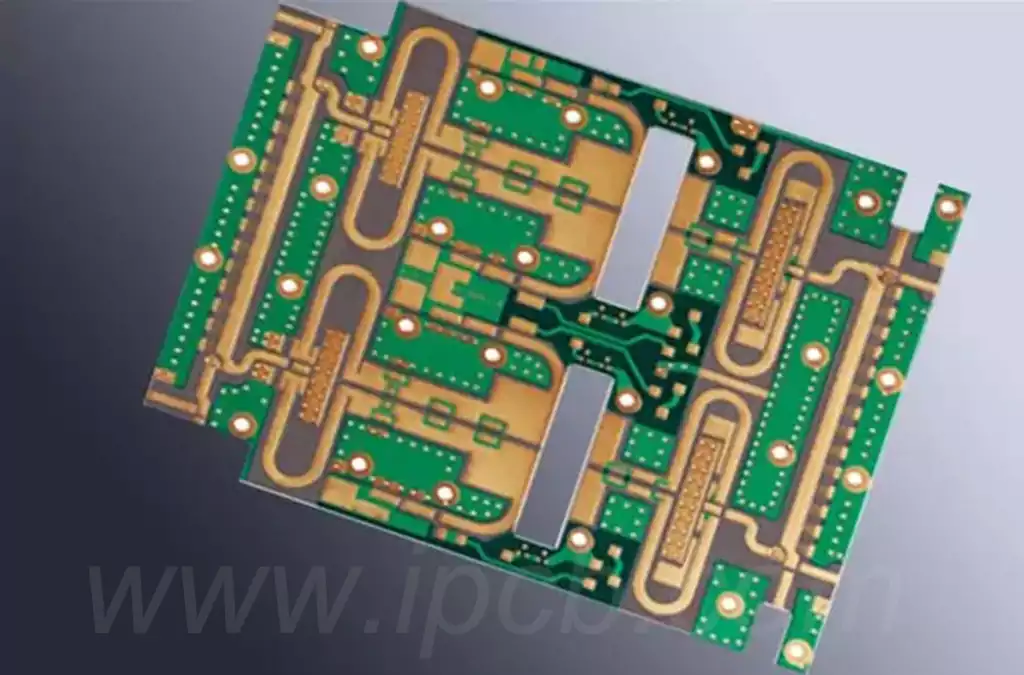

1) Superior high-frequency electrical properties. Glass is an insulating material with a dielectric constant approximately one-third that of silicon and a loss factor two to three orders of magnitude lower. This significantly reduces substrate loss and parasitic effects, ensuring signal integrity during transmission;

2) Large-format ultra-thin glass substrates are readily available. Glass manufacturers such as Corning, Asahi, and SCHOTT supply panel glass in oversized dimensions (>2m × 2m) and ultra-thin thicknesses (<50µm), alongside ultra-thin flexible glass materials.

3) Low cost. Benefiting from readily available large-format ultra-thin panel glass and the absence of insulation layer deposition, glass interposer fabrication costs are approximately one-eighth that of silicon-based interposers;

4) Simplified process flow. No insulation layer deposition is required on the substrate surface or TGV inner walls, and thinning is unnecessary for ultra-thin interposers;

5) High mechanical stability. Minimal warpage is maintained even when interposer thickness falls below 100µm;

6) Broad application scope. As an emerging vertical interconnect technology for wafer-level packaging, it offers a novel technical pathway to achieve the shortest distances and smallest pitches between chips. Possessing excellent electrical, thermal, and mechanical properties, it holds unique advantages in fields such as RF chips, high-end MEMS sensors, and high-density system integration. It stands as one of the preferred choices for 3D packaging of next-generation 5G and 6G high-frequency chips.

Through Glass Via technology, with its distinctive material advantages and process characteristics, is emerging as a significant development direction within advanced packaging. As the challenges of Moore’s Law become increasingly apparent, TGV offers a reliable solution for the high-density and miniaturisation of microelectronic devices by addressing the limitations of traditional silicon substrates. In the future, TGV technology is expected to play a pivotal role in enhancing electronic product performance and reducing manufacturing costs, further driving the advancement of 3D integration and high-frequency communication technologies.