Ceramic PCBs, with their superior thermal conductivity, high-temperature resistance and insulation properties, have become the core substrate for high-end electronic equipment. The quality of the routing process directly determines their performance and service life. Even with identical ceramic substrates and identical component configurations, improper routing can lead to signal crosstalk, impeded heat dissipation, mechanical stress concentration and other issues, potentially causing product failure.

Conversely, scientific routing design maximises the performance advantages of ceramic PCBs. How can efficient, reliable routing be achieved on ceramic PCBs? This requires balancing material properties, electrical requirements, and manufacturing processes, with precise control over every critical stage.

Characteristics of Ceramic PCBs

Ceramic PCBs exhibit fundamental material differences compared to traditional FR-4 PCBs. Routing designs that overlook these distinctions are highly prone to issues. Ceramic materials (such as aluminium oxide, aluminium nitride, and LTCC low-temperature co-fired ceramics) exhibit high hardness yet significant brittleness, with a thermal expansion coefficient (CTE) substantially lower than metals and organic substrates. They also possess extremely low dielectric loss and outstanding insulation properties. These characteristics dictate core principles for routing design: minimising mechanical stress, accommodating thermal expansion differences, leveraging high-frequency advantages, and ensuring manufacturability.

The high brittleness necessitates routing designs that minimise stress concentration within the substrate. Excessively long straight runs, overly acute corner angles, or abrupt changes in trace width may cause substrate cracking during manufacturing, soldering, or operation due to thermal expansion and contraction stresses. Conversely, the low dielectric loss advantage is ideal for high-frequency signal transmission. Routing designs can fully exploit this to optimise signal paths and reduce attenuation. Furthermore, ceramic substrates possess excellent thermal conductivity. Routing can be designed in conjunction with thermal management requirements, enabling synergistic integration of electrical connectivity and heat dissipation functions.

Four Core Routing Principles

Effective routing for ceramic PCBs must centre on four core principles: ‘line specifications, signal integrity, thermal synergy, and manufacturing adaptability.’ Each aspect requires balancing theoretical design with practical application scenarios.

1.Trace Specification Design: Aligning Electrical Requirements with Substrate Characteristics

Track width and spacing form the fundamental parameters of routing, requiring precise determination based on current magnitude, voltage levels, and manufacturing processes. For current carrying capacity, adhere to the principle of ‘wide tracks for high currents’: generally, a copper track width of no less than 1mm is recommended for 1A current (with ceramic PCBs typically employing copper layer thicknesses of 1-3oz). Should currents exceed 5A, further widening of tracks or a multi-track parallel design is necessary, alongside provision of adequate thermal clearance. Note that while copper adhesion to ceramic substrates is robust, excessively wide traces increase thermal stress on the substrate. This can be mitigated through a ‘segmented widening with transition radii’ design approach, balancing current carrying capacity and stress management.

Trace spacing must meet insulation requirements and voltage ratings, with higher voltages necessitating greater spacing: – Low-voltage signals (≤30V): recommended spacing ≥0.2mm – High-voltage signals (≥100V): spacing ≥0.5mm In high-humidity or harsh environments, spacing should be increased by over 30%. Furthermore, breakdown voltages vary across ceramic substrates. Aluminium nitride ceramics exhibit superior insulation properties compared to aluminium oxide. Trace spacing should be adjusted according to substrate type to prevent insulation failure.

Trace thickness selection must balance thermal and electrical conductivity requirements. The commonly used 1oz copper layer (approximately 35μm) on ceramic PCBs suffices for most medium-to-low power applications. while 2-3oz copper is recommended around high-power components to enhance current-carrying capacity and thermal conductivity. However, thicker copper traces present greater etching challenges and require manufacturing process coordination to prevent issues such as burred edges or copper layer delamination.

2.Signal Integrity Optimisation: Mitigating Crosstalk and Attenuation

Ceramic PCBs are frequently employed in high-frequency, high-speed signal applications, necessitating meticulous routing design to safeguard signal integrity. High-frequency signal transmission paths should adhere to the principles of ‘shortest, straightest, and fewest branches’ to minimise signal reflection and attenuation. Long, curved traces increase path length, exacerbating high-frequency signal loss. Employing 45-degree or curved corners instead of 90-degree right angles reduces the signal reflection coefficient.

Signal crosstalk is a common issue in high-frequency environments, requiring avoidance through proper routing isolation: different signal types (e.g., digital versus analogue, high-frequency versus low-frequency) should be routed in separate zones with spacing no less than three times the line width. Critical signals (e.g., clock signals, RF signals) necessitate shielded routing or ground planes surrounding them to form ‘signal isolation zones,’ thereby reducing electromagnetic interference. For differential signals, ensure both signal lines are of equal length and maintain uniform spacing to prevent signal skew caused by path differences, which could compromise signal synchronisation.

Furthermore, ground plane design is critical for signal integrity. Ceramic PCBs should employ a ‘large-area copper pour with multiple ground planes’ configuration to reduce ground resistance and potential differences. In high-frequency zones, ground planes must be tightly coupled with signal traces to form complete return paths, preventing interference caused by impeded signal return. Note that copper islands must be avoided during plating to prevent increased thermal stress on the substrate. This can be balanced by incorporating thermal isolation grooves or connection bridges to optimise copper coverage and stress distribution.

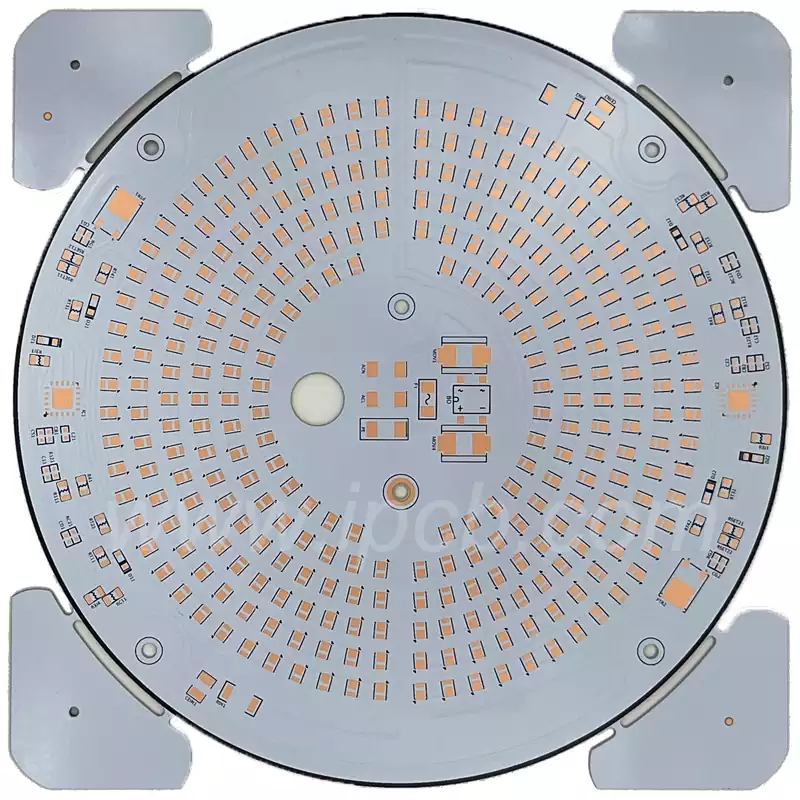

3.Thermal Synergy Design: Harnessing Routing for Heat Dissipation

One core advantage of ceramic PCBs is thermal conductivity. Routing design should leverage this to achieve synergistic optimisation of electrical connectivity and heat dissipation. For high-power components (e.g., IGBTs, RF power amplifiers), adopt a ‘radial’ pin routing approach where traces fan out from the component pins to increase heat dissipation surface area. Simultaneously, incorporate large copper pads around the component to rapidly conduct heat, which is then dissipated externally via the ceramic substrate’s thermal conductivity.

Routing should be logically partitioned by power density zones: wider trace spacing in high-power areas creates thermal pathways, while compact routing in low-power zones maximises space utilisation. Crucially, routing must avoid obstructing thermal pathways—such as ceramic PCB vent holes or heat sink mounting areas—ensuring these zones remain free of redundant traces to maintain thermal efficiency. For multilayer ceramic PCBs (e.g., LTCC), dedicated thermal layers may be incorporated internally. Through-holes can conduct surface heat to these inner thermal layers, achieving comprehensive heat dissipation.

4.Manufacturing Compatibility: Ensuring Design Realisation and Yield Assurance

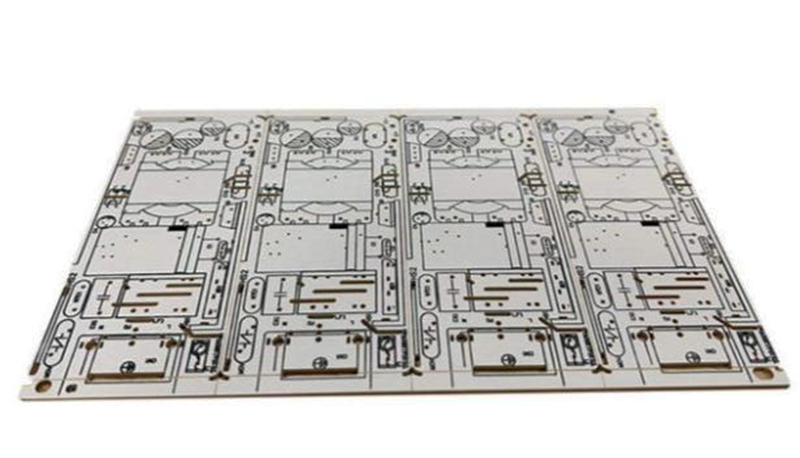

Excellent routing design must consider manufacturing feasibility to prevent yield degradation and cost escalation. Ceramic PCB manufacturing processes (e.g., DPC direct copper plating, LTCC co-firing, thick-film printing) impose specific routing requirements necessitating prior collaborative consultation.

For DPC-processed ceramic PCBs, minimum trace width/spacing can reach 20/20μm; however, edge smoothness must be maintained to prevent serration, which compromises copper layer adhesion. For LTCC process routing, co-firing shrinkage must be accounted for. Design must incorporate shrinkage allowance while minimising excessive line crossings to prevent voids or delamination during co-firing. Thick-film printing processes offer lower line width precision (minimum line width approximately 100μm). Routing design should avoid excessively fine lines and complex corners to ensure printing accuracy.

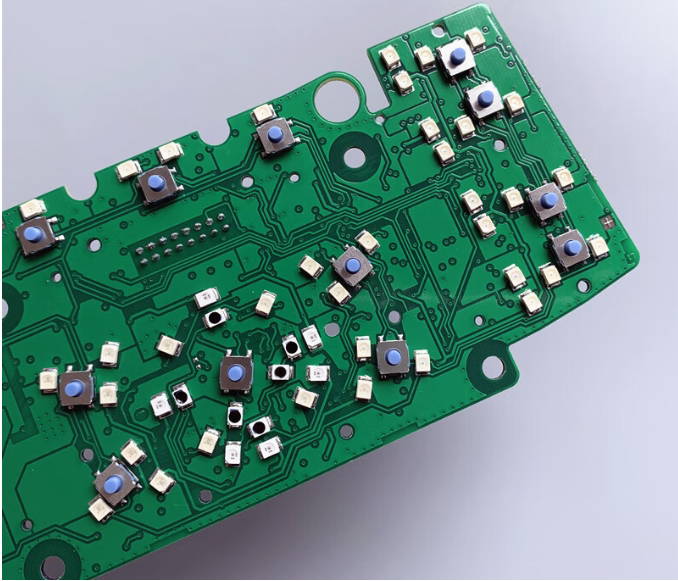

Furthermore, via design is crucial for manufacturing compatibility: ceramic PCBs utilise through-holes, blind vias, and buried vias. Through-holes present the lowest manufacturing complexity and cost, making them suitable for most applications. Blind and buried vias enhance space utilisation but involve more intricate processes and higher costs. Via diameters should correspond to trace widths, typically no less than 0.2mm, with spacing no less than 0.5mm to prevent excessive density compromising substrate strength.

Optimising Layout for Different Scenarios

The application scenarios for ceramic PCBs vary considerably. Layout design must be optimised specifically for each scenario’s requirements to achieve optimal results.

In high-frequency communication applications (e.g., 5G millimetre-wave filters, RF modules), routing must prioritise signal integrity: employ microstrip or stripline traces, strictly control characteristic impedance (e.g., 50Ω, 75Ω), and minimise signal reflection through impedance matching design. Trace routing should be as straight as possible, with curved transitions at corners to avoid signal attenuation. Strict isolation must be maintained between different RF channel traces to prevent crosstalk.

In high-power scenarios (e.g., new energy vehicle power electronics, industrial inverters), routing must prioritise thermal management and current carrying capacity: employ thick copper traces and large-area copper planes to enhance current handling and heat dissipation efficiency; power device pin routing should be short and wide to minimise trace impedance and heat generation; Ground connections should employ star-point or single-point grounding to prevent interference caused by ground potential differences. Additionally, sufficient thermal pathways must be reserved to ensure rapid heat dissipation.

In military/aerospace applications (e.g., satellite communications equipment, missile guidance systems), wiring must balance reliability with resistance to harsh environments: Circuit design should minimise stress concentration through rounded corners and tapered line widths to prevent substrate cracking; critical circuits should employ redundant design to enhance fault tolerance; concurrently, increased line spacing and insulation protection ensure stable operation under high temperatures, intense radiation, and severe vibration.

Routing Pitfall Avoidance Guide: Common Issues and Solutions

A series of problems frequently arise during actual routing. Proactively avoiding these and mastering solutions can significantly enhance design efficiency and product reliability.

Issue 1: Substrate Cracking. Primarily caused by stress concentration from circuit design. Solution: Avoid excessively long straight runs; incorporate micro-radius transitions every 5-10mm. Employ 45° or curved corners; prohibit 90° right angles. Prevent abrupt width changes with gradual transitions. Minimise large continuous copper pads and incorporate thermal isolation grooves.

Issue 2: Severe signal crosstalk. Primarily caused by insufficient trace spacing or improper signal zoning. Solution: Increase spacing between different signal types to at least three times the trace width; employ shielded traces or ground planes around critical signals; segregate high-frequency and low-frequency signals into distinct routing zones, avoiding cross-overlap.

Issue 3: Inadequate heat dissipation. Often caused by traces obstructing heat pathways or neglecting thermal considerations in layout. Solutions: Employ thick copper traces and large-area copper pads in high-power zones; avoid covering heat dissipation holes or heat sink mounting areas with traces; design radial traces to optimise thermal conduction paths.

Issue 4: Low manufacturing yield. Primarily due to design mismatch with manufacturing processes. Solutions: Determine minimum line width/spacing based on ceramic PCB manufacturing process (DPC/LTCC/thick film); ensure via diameter and spacing meet manufacturing requirements; avoid overly complex circuit designs to reduce manufacturing complexity.

Ceramic PCB routing design is not merely ‘connecting circuits’; it is a systematic engineering process integrating material properties, electrical requirements, thermal demands, and manufacturing processes. Only by precisely controlling the four core elements—circuit specifications, signal integrity, thermal coordination, and manufacturing adaptability—and implementing targeted optimisations for specific application scenarios, can the performance advantages of ceramic PCBs be fully realised to achieve efficient and reliable connections. Looking ahead, as ceramic PCB technology continues to advance, routing processes will evolve towards greater precision, efficiency, and intelligence, providing stronger impetus for innovation in high-end electronic devices.