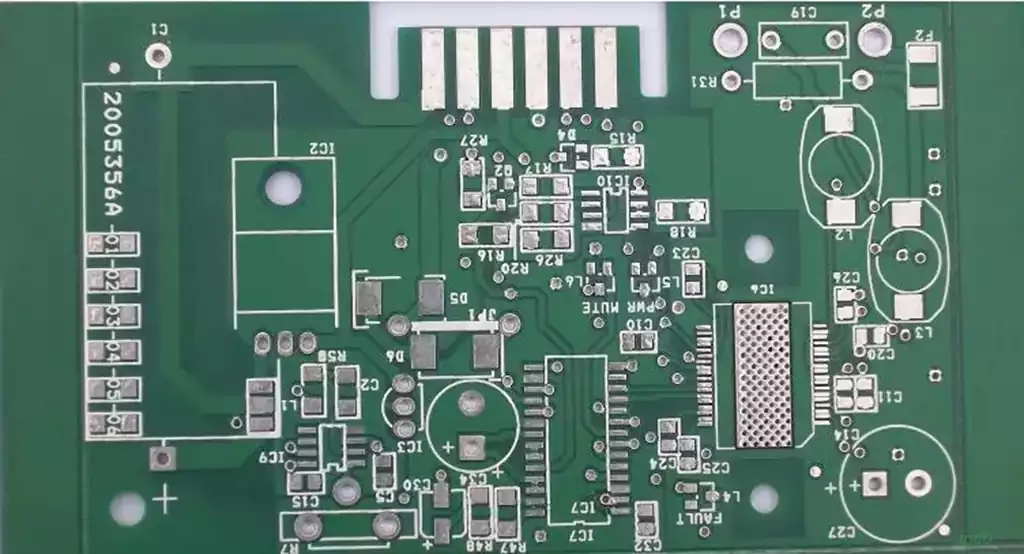

Vias are an important part of printed circuit board (PCB) design and have a significant impact on signal integrity and power integrity. Via impedance calculation not only relates to the signal transmission quality, but also directly affects the stability and performance of the circuit. In PCB layout design, a reasonable through-hole design and its impedance calculation can effectively reduce signal attenuation and reflection, thus improving the performance of the entire circuit.

If the via impedance mismatch, it will trigger signal reflection and attenuation phenomenon, which in turn adversely affects the overall performance of the circuit. Especially in high-speed digital circuits and RF circuits, the precise control of the through-hole impedance is particularly important because it is directly related to the integrity of the signal transmission and the reliability of the circuit.

Via impedance consists of two main components: series impedance and parallel impedance.The series impedance arises from the resistance and inductance of the through-hole conductor,while the parallel impedance arises from the capacitive effect between the through-hole and the neighboring medium.

The process of calculating via impedance takes into account a number of key factors,including the geometry of the via, the material properties, and the laminated configuration of the PCB.The following is the basic procedure for performing vias impedance calculation:

- Define vias specifications: This includes determining the diameter (D) of the vias, the internal aperture (d), and the size of the pads (Dp). These size parameters are critical for subsequent impedance calculations.

- Calculate the perforation resistance value: Using the resistivity (ρ) information of the perforation material, the DC resistance (R) of the perforation can be derived by the following formula: R = ρ × L / A. In this formula, L represents the length of the perforation and A is the cross-sectional area of the perforation. Taking FR4 sheet as an example, the resistivity of a copper conductor at 20°C is about 1.7 × 10^-8 Ω-m.

- Estimation of perforation inductance: The inductance (L) of the perforation can be estimated by the following formula: L = (μ0 × μr × D) / [2 × ln(D/d) + 0.4]. Here, μ0 represents the magnetic permeability of the vacuum and μr is the relative magnetic permeability of the PCB material. μ0 has a value of 4π × 10^-7 H/m (Henry per meter). For FR4 PCB materials, the relative permeability μr is usually close to 1, i.e., its permeability is similar to that of vacuum.

- Calculate the perforation capacitance: The capacitance (C) of the perforation can be calculated by the following formula: C = (ε0 × εr × D) / [ln(D/2d) + 0.8]. In this formula, ε0 represents the capacitance of the vacuum, while εr is the relative capacitance of the PCB material.

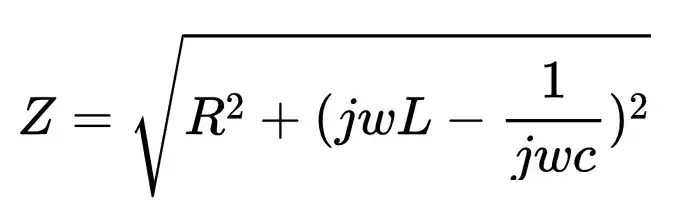

- Calculate the total impedance: The values of resistance and inductance are converted to impedance (Z), and the influence brought by capacitive effect is considered at the same time, so as to derive the comprehensive impedance value of the vias.

where ω is the angular frequency and j is the imaginary unit.

Over-hole design considerations

- Vias Size Selection

When designing a PCB, the size selection of the vias is very critical. Typically, for multi-layer PCBs, the recommended via diameter and pad size should be based on the specific application. In general, for 6-10 layer PCBs, using 10/20Mil (vias/pad) size is a more reasonable choice to help balance signal quality and cost.

When designing high-density small-sized circuit boards, you can consider using 8/18Mil smaller sizes, although it should be noted that under current technical conditions, too small a size may lead to processing difficulties.

- Reduce the signal layer change

In the design,the signal alignment layer change will increase the signal transmission delay and loss, so should minimize the signal alignment layer change.Each signal layer change may introduce additional parasitic inductance and capacitance,affecting signal integrity.Therefore,it is better to plan the signal path by layer and reduce the number of vias during design to maintain the signal quality and transmission speed. - Power and ground via design

In power and ground design, punch holes as close as possible to ensure that the leads between the vias and the pins are as short as possible to reduce inductance. Leads too long will increase impedance, affecting the stability of the signal. In addition,consideration should be given to arranging the ground vias together with the signal vias to improve the ground loop and thus reduce parasitic effects. - Volume and interlayer distance

In PCB design, the volume of vias and the distance between layers also need to be reasonably planned.The number and size of vias will directly affect the volume and material cost of the PCB, so appropriate trade-offs should be made in the design.Too large a density of vias may lead to the formation of broken copper layer grooves, thus affecting the electrical connection.Designers should be flexible according to the specific circuit requirements, to avoid the over-hole arrangement of the density is too high. - Consider parasitic effects

When transmitting signals, we also need to consider the parasitic effects brought about by the vias. Parasitic inductance and capacitance can affect the signal transmission characteristics, which may lead to reflections and delays. Designers should pay attention to these effects and minimize additional vias in the signal routing to reduce the negative impact of parasitic effects.

Accurate calculation and optimization of via impedance is the key to improving PCB performance. Properly designed vias size, layout, and consideration of parasitic effects can significantly reduce signal attenuation and reflection, ensuring signal integrity and circuit stability. These strategies are critical to meeting the high-speed, high-reliability demands of modern electronic devices.