Thermal stress refers to the mechanical stress arising from uneven thermal expansion or contraction within materials during temperature changes. Within the PCB substrate sector, thermal stress primarily originates from the following sources:

Thermal cycling during manufacturing

Reflow Soldering: In SMT processes, PCB substrate endure high temperatures (240–260°C) and rapid cooling. Non-uniform expansion and contraction of materials may cause interlayer delamination or copper foil lifting.

Wave Soldering: Through-hole components undergo this process, facing thermal stress from the 260°C thermal shock.

Hot Air Solder Leveling (HASL): During this process, PCB substrates are immersed in molten solder at high temperatures, followed by high-pressure hot air to remove excess solder. This may cause copper foil delamination or substrate deformation.

Environmental Temperature Variations

Heat accumulation during device operation, particularly from high-power chips or modules, may cause localised overheating. Equipment operating across diverse environmental temperatures—such as outdoor communications, automotive electronics, and aerospace applications—faces temperature ranges from -40°C to +125°C or wider. Temperature differentials during device power cycling, such as cold starts in servers, induce repeated expansion and contraction of PCB board materials, generating fatigue stresses.

Localised Hotspots from Power Density

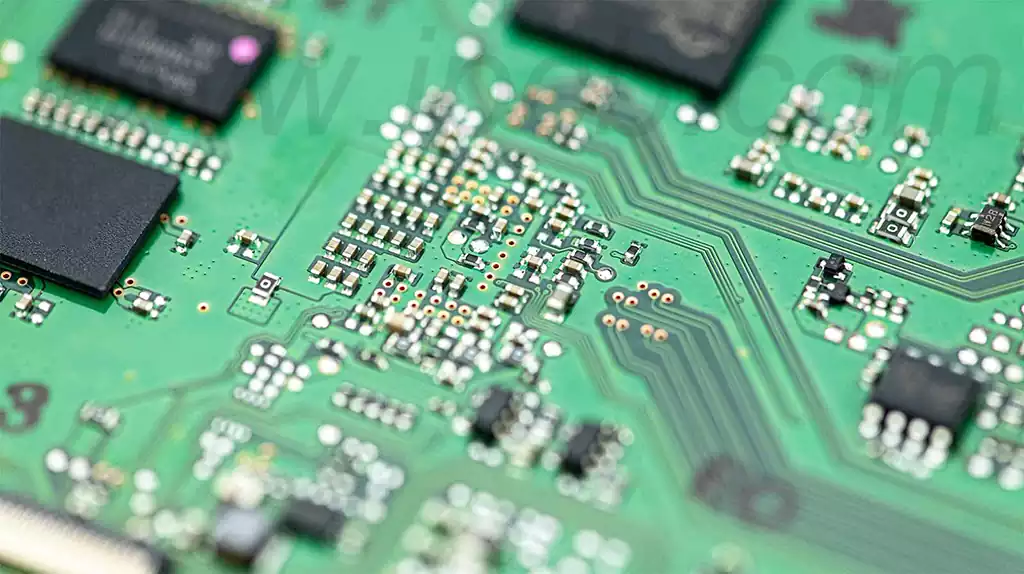

The drive towards miniaturisation and high performance in electronics increases PCB power density, creating localised hotspots. Temperature gradients in these areas generate thermal stresses due to limitations in PCB material thermal conductivity, potentially causing warping or solder joint failure.

Effects of Thermal Stress

PCB substrates subjected to prolonged thermal stress face multiple reliability challenges. These effects include:

Delamination

The primary cause of interlayer separation is the mismatch in coefficient of thermal expansion (CTE) between the PCB substrate and copper foil. When exposed to high temperatures, laminate materials may delaminate due to stress, temperature fluctuations, or manufacturing defects, sometimes accompanied by blistering or cracking of the board. Excessive humidity exacerbates PCB delamination, as moisture ingress between layers causes separation and peeling, leaving watermarks upon evaporation. Furthermore, excessive thermal expansion of the substrate during soldering or weak interfacial bonding can induce interface separation. If the CTE difference between the substrate and copper foil exceeds 3 ppm/°C, internal stresses generated during thermal cycling can directly compromise the bonding strength at the hole walls. Delamination and blistering are explicitly defined by the IPC-A-610 standard as localised expansion and separation between layers of the laminate substrate, or between the substrate and conductive films or protective layers.

Solder Joint Failure

In BGA (Ball Grid Array) packaging, solder joint failure represents one of the most prevalent failure modes. These joints develop fatigue cracks due to prolonged thermal cycling, subsequently causing electrical connectivity issues. For instance, mobile phone motherboard case studies indicate that 87% of BGA cracks occur after 600 thermal cycles. Discrepancies in the Coefficient of Thermal Expansion (CTE) between materials—such as a PCB’s CTE of 14-16 ppm/°C versus a BGA substrate’s CTE as high as 20-25 ppm/°C—subject solder joints to shear stress during temperature changes, leading to cracking. Common manifestations of BGA solder joint failure include crack initiation, joint fracture, and intermetallic compound (IMC) failure. Solder voiding may also occur, such as when device balls or PCB pads oxidise, preventing robust metallurgical bonding between solder and pads. Excessively rapid reflow cooling rates (exceeding 3°C/s) or high impurity content in solder (e.g., copper exceeding 0.5%) may also induce internal stresses within joints or increase brittleness, predisposing them to fracture.

Copper Conductor and Via Fracturing

Copper conductors and vias may develop cracks during repeated thermal cycling due to thermal expansion and contraction. In high-density interconnect (HDI) PCBs, smaller via dimensions coupled with insufficient copper filling can concentrate thermal stresses, heightening failure risks. Particularly in microvias for flip-chip packaging, process-related defects at copper layer interfaces may cause cracks to initiate from microvia edges. Via failure is a typical defect in HDI PCBs, typically manifesting as increased via resistance or complete open circuits. Following thermal cycling tests, common defects manifest as plated copper cracks. Neither IPC6012C Class 2 nor Class 3 standards permit plating cracks. Oxidation layers on copper strands exacerbate stress concentration, reducing fatigue crack initiation life under cyclic loading by over 50%.

PCB Warping

PCB boards comprise diverse materials such as copper foil, resin, and glass cloth, each possessing distinct physical and chemical properties. During lamination, residual thermal stresses develop, inducing PCB deformation. Mismatched thermal expansion coefficients between the substrate and copper layers are key factors causing warping and distortion. Such deformation not only compromises component placement accuracy but may also trigger connector failures. In multilayer or large-format PCBs, this deformation effect becomes particularly pronounced due to differing thermal expansion and contraction rates across layers. For instance, excessive thermal expansion and contraction of the substrate can cause plated-through holes along the PCB’s Z-axis to twist and undergo plastic deformation, simultaneously distorting the copper pads on the PCB surface. The Coefficient of Thermal Expansion (CTE) is defined as the ratio of length increase to original length per unit temperature change, commonly used to measure PCB substrate thermal expansion properties.

Thermal Management Optimisation Solutions

- Material Upgrades: Employ high-thermal-conductivity resin substrates or metal substrates, elevating thermal conductivity to the 1–4 W/m·K range

- Structural Enhancements: Optimise crimp terminal designs and implement surface gold plating to reduce contact resistance

- Enhanced Heat Dissipation: Position heat sinks or heat pipes in critical heat-generating zones; introduce forced air cooling systems where necessary

- Layout optimisation: Adhere to thermal isolation principles for sensitive components, establishing dedicated thermal pathway design specifications

Thermal stress constitutes a critical factor in PCB design and manufacturing, posing significant challenges to long-term reliability. To effectively address thermal stress-related issues, a comprehensive thermal management optimisation strategy is required.