In the efficiency race of power electronics systems, engineers often focus on “front-end parameters” such as the on-resistance, gate charge, and reverse recovery charge of switching devices. However, a deeper, more fundamental factor—the “Substrate Diode“—whose impact is amplified after system integration, is often the hidden battleground determining the performance ceiling and long-term reliability of the final product.

The “Substrate Diode” here has two interrelated technical connotations: first, the parasitic diode inherent within power MOSFETs (such as silicon-based or silicon carbide-based MOSFETs); second, the high-performance insulating metal substrate that carries and interconnects these bare dies.

This article will move beyond generalities and delve into the physical mechanisms of devices and the cross-scale coupling of packaging, revealing the complete technology chain from chip design and package selection to system failure, and providing practical design considerations.

Microscopic Battlefield: Physical Mechanism and Switching Behavior of Parasitic Body Diodes in Power MOSFETs

Structural Origin and Basic Characteristics

In vertical power MOSFETs, the PN junction formed by the P-type body region and the N-epitaxial layer/substrate creates a parasitic diode, also known as the body diode, that is connected in reverse parallel to the MOSFET source-drain path. In bridge topologies, this diode provides a freewheeling path for the inductor current, but its performance is not optimized for high-frequency switching.

Its forward voltage drop is determined by the material’s bandgap, carrier lifetime, and structural design. For example, the body diode voltage drop of a traditional silicon-based MOSFET is approximately 1.2-1.5V, while the typical value for a silicon carbide Schottky barrier diode is only around 1.0V, which is one of the key factors contributing to the efficiency advantage of SiC MOSFETs.

Reverse Recovery: The Root of Losses and Noise

The most critical dynamic characteristic of the body diode is reverse recovery. When a diode switches from forward conduction to reverse blocking, minority carriers stored in the drift region need to be pumped out or recombine, generating a brief but high-amplitude reverse recovery current. This process is accompanied by significant switching losses and voltage overshoot.

Reverse recovery charge is a core parameter for evaluating the characteristics of a body diode. Due to the extremely short minority carrier lifetime of silicon carbide devices, the reverse recovery charge of the body diode is almost negligible, which is the theoretical basis for its ability to achieve ultra-high switching frequencies. Engineers must accurately measure the reverse recovery waveform of the body diode during double-pulse testing to assess its losses and stress under real-world operating conditions.

Third Quadrant Operation and Failure Modes

In applications such as synchronous rectification, the body diode experiences “third quadrant operation.” If the drive design is inappropriate, applying a gate voltage before the body diode is fully turned off, causing it to enter synchronous rectification mode, may lead to the risk of “bridge arm shoot-through.”

More insidious failures are related to bipolar degradation: In SiC MOSFETs, minority carrier injection in the body diode can induce the propagation of surface dislocations, causing the device’s on-resistance to drift over time. This is a long-term risk that must be assessed in high-reliability designs. Therefore, in automotive or industrial applications, even when using SiC MOSFETs, a high-performance SiC SBD is sometimes externally added to completely avoid body diode operation, thereby ensuring the highest long-term reliability.

Mesoscopic Bridge: DBC/AMB Substrate—Thermal, Mechanical, and Electrical Coupling Interface

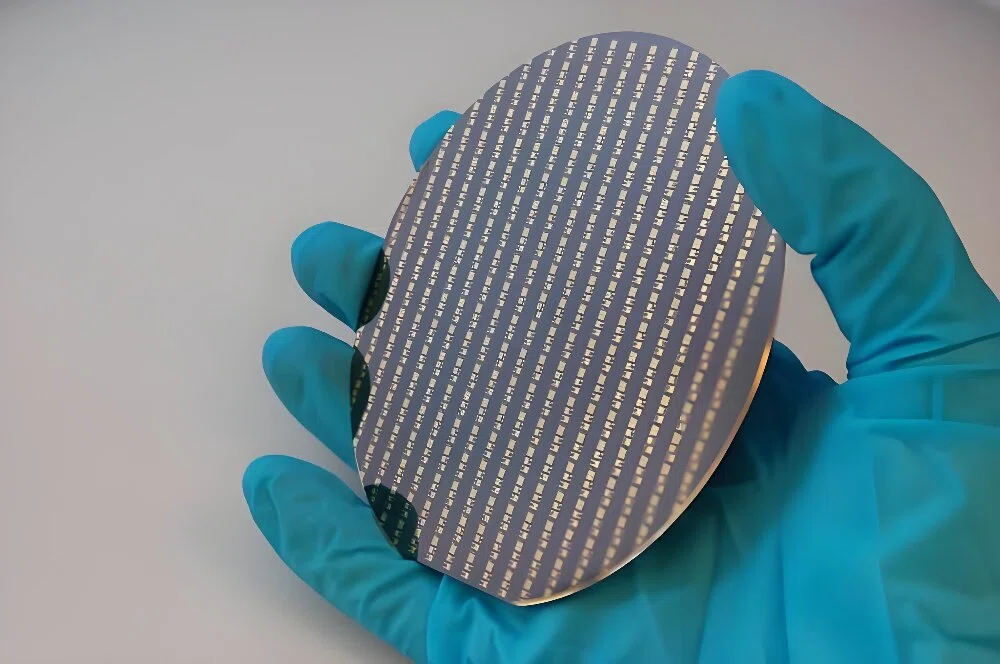

Material Selection: Alumina vs. Aluminum Nitride vs. Silicon Nitride

The insulating metal substrate carrying the power chip is the physical core of the “Substrate” concept. Direct copper-clad ceramic substrates are the mainstream choice, with the core being the ceramic layer material:

Al₂O₃: Lowest cost, thermal conductivity approximately 24-28 W/(m·K), good mechanical strength, but heat dissipation becomes a bottleneck at high power densities.

AlN: With a thermal conductivity as high as 170-200 W/(m·K), more than 7 times that of Al₂O₃, it has a better match with the thermal expansion coefficients of Si and SiC, but it is expensive and sensitive to process requirements.

Si₃N₄: Possesses excellent bending strength and fracture toughness, with a thermal conductivity of approximately 60-90 W/(m·K), making it the best choice for withstanding harsh power cycling and thermal cycling stresses, especially suitable for high-speed rail, wind power, and other fields requiring ultra-high reliability.

AMB is an upgraded process of DBC, using active solder to achieve the connection between copper and ceramic, resulting in higher bonding strength and the ability to withstand more severe temperature shocks.

Thermal Design and Failure Physics: From Junction Temperature to Thermal Cycling Fatigue

The DBC/AMB substrate constitutes a key link in the thermal resistance network between the chip and the heat sink. Its thermal conductivity, thickness, and area determine the thermal resistance from the junction to the casing. Improper design can lead to excessively high chip junction temperatures, accelerating electron migration, gate oxide degradation, and other failures. More complex failure modes stem from thermo-mechanical fatigue.

During power cycling, the multi-layered structure consisting of the chip, solder, DBC copper layer, ceramic, baseplate, TIM material, and heat sink experiences cyclic shear stress due to CTE mismatch. This stress first accumulates at the weakest point—usually the chip solder layer or the interface between the DBC copper layer and the ceramic—ultimately leading to solder layer cracking, increased void ratio (increased thermal resistance), or copper layer peeling off from the ceramic. Active metal brazing (AMB) technology, due to its stronger interfacial bonding, can significantly delay peeling failure, extending the lifespan of the power module by an order of magnitude.

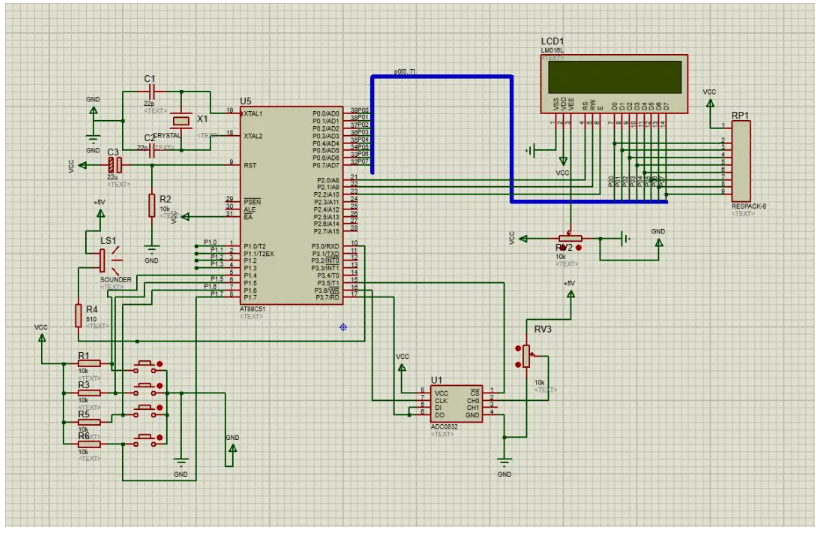

Electrical Parasitic Parameters and Layout Optimization: The copper layer on the DBC is etched to form the main circuitry and gate drive loop. Its layout directly determines the parasitic inductance of the power loop. Excessive loop inductance can generate severe voltage oscillations and overshoots during high-speed switching, threatening gate reliability and increasing EMI. Optimized designs include: using a multilayer busbar structure to minimize loop area; strictly separating the gate drive loop from the power loop; and achieving coaxial or surface current structures in the DBC layout whenever possible. For multi-chip parallel modules, the symmetry design of the DBC (Diode-Based Circuit) is crucial for achieving current sharing.

System-Level Challenges: Multiphysics Simulation and Testing

Collaborative Design and Simulation Process

Modern power module design relies on multiphysics simulation. The process typically begins with electro-thermal co-simulation: a circuit containing an accurate bulk diode model is built in software such as PLECS and Simetrix for loss calculation; then, the loss distribution map is used as a heat source and imported into CFD tools such as ANSYS Icepak and FloTHERM, or finite element software such as COMSOL, for 3D thermal simulation to obtain the junction temperature distribution; finally, the thermal cycling load is imported into structural mechanics simulation for fatigue life prediction. Electro-thermal-mechanical coupling simulation is the gold standard for evaluating the reliability of modules under real-world operating conditions.

Key Testing and Failure Analysis

Design verification relies on a series of rigorous tests:

Double-Pulse Test: Precisely measures the reverse recovery characteristics, switching losses, and voltage stress of the bulk diode.

Power Cycling Test: According to industry standards, under controlled junction temperature fluctuations, continuous switching is performed, monitoring changes in thermal resistance until failure, to evaluate the reliability of the solder layer and substrate interface.

Thermal Resistance Testing: Thermal resistance parameters from junction to casing and junction to environment are obtained through TSEP or transient thermal testing.

Failure Analysis: Techniques such as X-ray diffraction, scanning acoustic microscopy, and metallographic sectioning are used to locate weld voids, cracks, and interface delamination, providing feedback to design and process control.

Cutting-Edge Evolution and Selection Strategies

The Paradigm Shift Brought by Wide Bandgap Semiconductors: The widespread adoption of silicon carbide (SiC) and gallium nitride (GaN) has fundamentally changed the “substrate” ecosystem. The high operating junction temperature of SiC requires substrates with higher thermal conductivity, driving AlN and Si₃N₄ substrates to become standard. Although GaN-on-Si devices are integrated with the silicon substrate through epitaxial layers, their extremely high switching speed at the packaging level makes low parasitic inductance packaging a primary challenge, giving rise to new “substrate” forms such as copper pillar interconnects and fan-out packaging. Silver sintering, as a next-generation chip mounting technology, offers higher operating temperatures and lower thermal resistance, posing new requirements for the surface roughness and metallization of DBC/AMB substrates.

System Integration and Cost Trade-offs

In cost-sensitive applications, alumina DBCs remain the mainstream due to their mature supply chain. However, for fields prioritizing power density and lifespan, AMB-Si₃N₄ combinations are becoming the “gold standard” for high-performance modules, despite their cost being 5-8 times that of Al₂O₃ DBCs. Engineers must weigh the higher initial material costs within the framework of total system cost: can these costs be offset by increasing power density (reducing heatsink size), improving efficiency (reducing operating electricity costs), or extending maintenance-free lifespan? This is no longer a simple technical choice but a comprehensive business decision.

Looking Ahead: From Discrete to Integrated

In the future, substrates are evolving from passive carrier platforms to active system integration platforms. For example, in smart power modules, DBCs integrate not only IGBTs and diode chips but also driver ICs, current/temperature sensors, and even some passive components, forming a complete “power electronics core.” The substrate itself may integrate thin-film capacitors, planar transformers, and even cooling channels, evolving into a “functionally integrated substrate.” At this point, the “Substrate Diode” has been fully integrated into a highly integrated system solution.

Summary: Building a System-Level Engineering Mindset

The concept of the “Substrate Diode,” from the parasitic PN junction of the chip to the insulating metal substrate of the module, perfectly illustrates the complexity of power electronic system design: microscopic physical mechanisms determine macroscopic performance boundaries, and macroscopic packaging constraints define microscopic operating limits.

For design engineers, it is no longer possible to view the body diode parameters on the chip datasheet in isolation, or to treat the DBC substrate as a simple heatsink. A system-level, end-to-end engineering mindset must be established:

In the early stages of design, the switching behavior of the body diode should be incorporated into topology selection and loss modeling.

During package selection, based on thermal simulation and lifetime prediction results, an informed choice should be made between Al₂O₃, AlN, and Si₃N₄, and the electrical layout of the DBC should be optimized.

In testing and verification, beyond conventional static parameter testing, in-depth dynamic switching, power cycling, and failure analysis should be conducted to understand the physical root causes of failure.

Ultimately, a deep understanding and precise control of the “Substrate Diode” is the key bridge to transforming an excellent power chip into a superior, reliable, and competitive power product. This requires engineers to traverse multiple knowledge boundaries across semiconductor physics, materials science, heat transfer, mechanics, and electrical engineering, which is precisely where the allure and challenge of power electronics design lie.