The design of thick copper PCBs differs significantly from that of conventional thin copper PCBs. The core challenge lies in ‘balancing high current-carrying capacity, efficient heat dissipation and manufacturing feasibility’—line width calculations must take into account both current-carrying capacity and etching processes, via design must avoid voids, and thermal management must utilise the advantages of thick copper without causing localised overheating. Applying thin-copper design principles (such as designing 3oz trace widths based on 1oz current-carrying standards) will result in either excessively wide traces that waste space, or excessively narrow traces that cause overheating.

Trace Width and Spacing Design: Controlling Both Current-Carrying Capacity and Process Limits

Thick-copper trace widths must simultaneously meet ‘current-carrying requirements’ and ‘manufacturing process limits’ to avoid defects caused by single-dimensional calculations:

1.Trace Width Calculation: Dual Standards for Current Carrying Capacity and Heat Dissipation

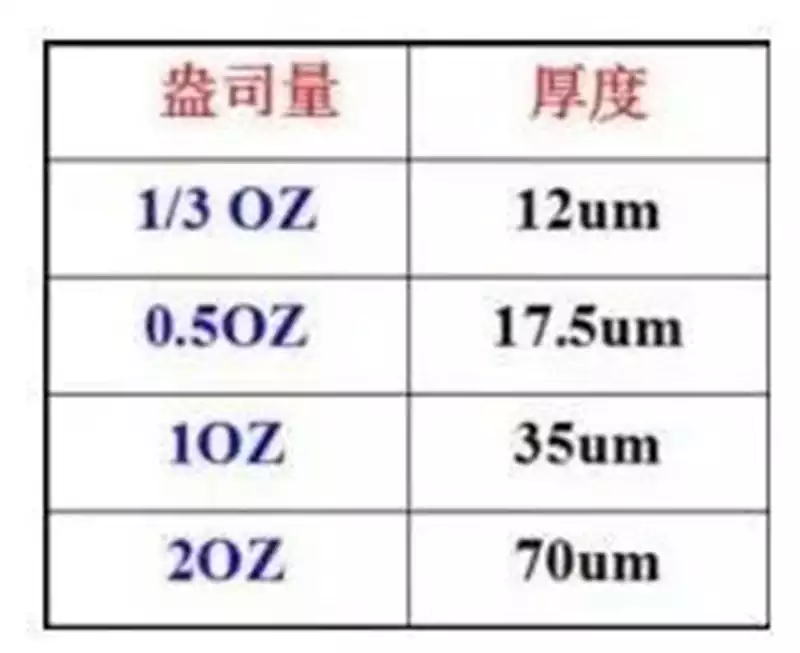

Current Carrying Capacity Standard: For thick copper PCBs, trace width is estimated using the formula “copper foil thickness × trace width = current carrying capacity”, with the core formula being:

Trace Width (mm) = Current (A) ÷ (Copper Foil Thickness (oz) × 0.33)

Example: 3 oz copper foil carrying a 10 A current; trace width = 10 ÷ (3 × 0.33) ≈ 10.1 mm (rounded to 10 mm, allowing a 10% margin);

Comparison: 1 oz copper foil carrying 10 A requires a trace width of 30.3 mm; thick copper can significantly reduce the space occupied by traces;

Heat dissipation supplement: High-current (>5A) traces require an additional 20%–30% width to prevent localised overheating (e.g. for a 3oz copper foil trace carrying 10A, the current-carrying capacity calculation requires 10mm; considering heat dissipation, use 12mm);

Processing limits: The minimum etched trace width for thick copper is ≥0.5mm (3 oz) and ≥0.8mm (5 oz); traces that are too narrow are prone to uneven etching (copper residue or over-etching).

2.Spacing Design: Creepage Distance and Manufacturing Feasibility

Current-related spacing:

Low-voltage (≤30V) high-current circuits: Spacing ≥ line width (e.g. for a 10mm line width, spacing ≥ 10mm), to avoid interference caused by current coupling;

High-voltage (>100V) circuits: Spacing ≥ 0.1mm/V (e.g. for a 220V circuit, spacing ≥ 22mm), whilst also meeting creepage distance requirements;

Manufacturing-related spacing: Thick copper etching involves significant undercut (10–20 μm), so spacing must be 20% greater than for thin-copper PCBs (e.g. for a 0.2 mm spacing on thin copper, 0.24 mm is required on thick copper) to prevent short circuits after etching.

Via Design: Avoiding Voids and Ensuring Electrical Continuity

The challenge in manufacturing vias on thick-copper PCBs lies in the ‘bonding between the thick copper layer and the via plating’, which is prone to voids and uneven plating; therefore, the design requires targeted optimisation:

1.Via Dimensions and Pads

Via diameter selection:

3 oz copper foil: minimum hole diameter ≥ 0.6 mm (typically 0.8 mm), pad diameter ≥ hole diameter + 0.4 mm (e.g. for a 0.8 mm hole, the pad should be 1.2 mm);

5 oz and above: minimum hole diameter ≥ 1.0 mm, pad diameter ≥ hole diameter + 0.6 mm, to prevent thick copper from covering the via and causing plating difficulties;

Number of Vias: High-current circuits require “a large number of evenly distributed” vias; at least 2 vias per 1A of current (e.g. a 10A circuit requires ≥20 vias), with a spacing of ≥2mm between vias to prevent vias from burning out due to current concentration.

2.Via Plating and Filling

Plating thickness: The plating thickness on the inner walls of vias must be ≥25μm (50% higher than for thin-copper PCBs) to ensure electrical conductivity and mechanical strength;

Filling options:

High-current vias (>5A): Use resin filling + copper plating (full filling) to prevent poor heat dissipation caused by air pockets inside the via;

Standard vias: Semi-filling may be used, but ensure complete plating coverage with no exposed substrate.

Substrate and Layer Stack Design: Adapting to Thick Copper Characteristics

Thick copper PCB substrates and layer stacks must withstand greater thermal and mechanical stresses; design must prioritise stability:

1.Substrate Selection

Tg value: Select high-Tg substrates (Tg ≥ 170°C; conventional thin-copper PCBs require Tg ≥ 130°C) to prevent substrate softening at high temperatures, which could lead to copper foil delamination;

Thermal conductivity: For industrial applications, select high-thermal-conductivity FR-4 with a thermal conductivity of ≥1.0 W/(m·K); for new energy applications, metal-based substrates (e.g. aluminium-based, with a thermal conductivity of 200 W/(m·K)) may be used;

Chemical resistance: The substrate must withstand the alkaline etching solution (pH 8–9) used in thick copper etching to prevent substrate swelling during the etching process.

2.Layer Stack Design

Symmetry principle: Multi-layer thick copper PCBs require a symmetrical layout (e.g. “thin copper – thick copper – substrate – thick copper – thin copper”) to prevent warping caused by thermal expansion differences after lamination;

Copper foil distribution: Thick copper layers should be positioned as close as possible to the PCB surface to minimise heat transfer pathways (e.g. in applications with high heat dissipation requirements, place the thick copper layer on the top layer to ensure direct contact with the heat sink);

Example: 4-layer thick copper PCB (3 oz) stack-up: Top layer (3 oz thick copper) → substrate (1.0 mm, Tg 170°C) → inner layer (1 oz thin copper, signal layer) → substrate (1.0 mm) → bottom layer (3 oz thick copper).

Thermal management design: Maximising the heat dissipation advantages of thick copper

One of the core benefits of thick copper PCBs is efficient heat dissipation; the design must actively guide heat transfer to avoid localised hotspots:

1.Layout Optimisation

High-power components: Mount heat-generating components such as power transistors and DC-DC converters (power dissipation > 1W) directly onto the thick copper area, ensuring the copper foil area is at least three times the component package area (e.g., for a TO-220 package, the thick copper area should be ≥15mm × 10mm);

Heat Dispersion: Avoid concentrating high-current circuits; adopt ‘mesh’ or ‘tree-like’ routing to distribute current across multiple thick copper traces, thereby reducing heat generation in individual traces.

2.Auxiliary Heat Dissipation Structures

Windows in thick copper areas: Create windows (without solder mask) in thick copper areas where no components are mounted, directly exposing the copper foil to enhance convective heat dissipation efficiency (heat dissipation efficiency improves by 25% after creating windows);

Heat sink attachment: Reserve mounting holes for heat sinks in thick copper areas (hole diameter matching screws, e.g. M3). Apply thermal grease (thermal conductivity ≥5 W/(m·K)) between the heat sink and the thick copper to reduce contact thermal resistance.

The essence of thick copper PCB design lies in striking a balance between high current carrying capacity, efficient heat dissipation and manufacturability. Only by simultaneously addressing current-carrying calculations, etching limits, via reliability and thermal management optimisation can the advantages of thick copper be fully realised, thereby avoiding performance or reliability issues caused by applying thin copper design principles.