As electronic products continue to evolve towards lighter, thinner designs and higher levels of integration, hardware design is no longer confined to simple two- or four-layer boards. 6 layer PCBs (six-layer printed circuit boards), as a compromise solution that balances performance, size, cost and structural stability in complex circuit designs, have become one of the most widely used multilayer boards in the industry.

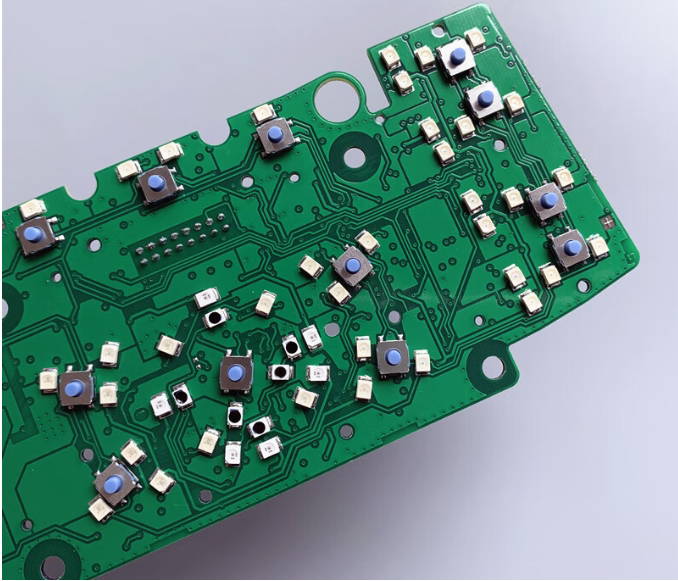

In practical development, mid-to-high-end industrial equipment, in-vehicle auxiliary control units, high-speed communication modules and similar applications almost universally utilise 6 layer pcbs. The multi-layer, separated structure allows for the independent partitioning of signal, power and ground layers, effectively resolving the issues of signal crosstalk and power supply noise commonly found in boards with fewer layers.

What is a 6 layer PCB?

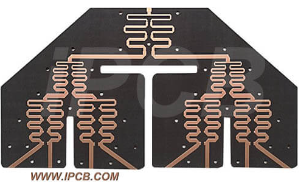

A 6 layer pcb consists of six copper conductive layers. The layers are electrically isolated from one another by semi-cured sheets (PP sheets) and core boards, and are bonded together under high temperature to form a single unit. This represents a mature, mass-production process for multilayer PCBs.

Compared to four-layer boards with limited routing space, the two additional inner layers can be used to flexibly add independent ground or power planes. This layout stabilises the supply voltage and shortens the return path for high-speed signals, thereby significantly reducing electromagnetic interference (EMI). For projects requiring moderate high-speed signal transmission but not necessitating high-end boards with eight or more layers, the six-layer structure offers the best value for money.

6 layer PCB Stack-Up Schemes

Scheme 1: Signal Layer Priority (Focus on High-Speed Signal Integrity)

Top Layer (Layer 1): Signal layer. Used for routing critical high-speed signal lines, important control lines, clock lines and surface-mount components. Typically, the top layer has the highest routing density.

Inner Layer 1 (Layer 2): Ground plane (GND). Provides a low-impedance return path for top-layer signals, whilst shielding top-layer noise and reducing EMI radiation; it serves as a critical reference plane for high-speed signal routing.

Inner Layer 2 (Layer 3): Signal layer. Used for internal routing of medium-to-low-speed signals or general control lines, typically using Layer 2 or Layer 4 as the reference plane.

Inner Layer 3 (Layer 4): Signal layer. Its function is similar to that of Layer 3, and it typically uses Layer 3 or Layer 5 as its reference plane.

Inner Layer 4 (Layer 5): Power plane (VCC). It provides a low-impedance distribution network for the main power supply (such as VCC, VDD) and, when appropriately partitioned, can accommodate a small number of secondary power supplies. It also serves as a reference for Layer 4 and the bottom layer (Layer 6).

Bottom Layer (Layer 6): Signal layer. Used for routing medium- and low-speed signals, remaining control lines, test points, through-hole connectors and some surface-mount components; the routing density is typically lower than that of the top layer.

Advantages:

The top and bottom layers each have a complete ground plane (Layer 2) or power plane (Layer 5) as a reference, making them highly suitable for routing critical high-speed signals (such as DDR and SerDes differential pairs) on the surface layers.

The four signal layers (L1, L3, L4, L6) are separated by the ground plane (L2) and power plane (L5), effectively reducing crosstalk between layers.

The ground plane (L2) and power plane (L5) are adjacent, forming a natural surface capacitance, which is beneficial for high-frequency decoupling and filtering.

EMI shielding performance is good (outer-layer signals are enclosed by the ground plane or power plane).

Scheme 2: Power Integrity Priority (Focusing on multi-power supply or complex power requirements)

Top Layer (Layer 1): Signal layer.

Inner Layer 1 (Layer 2): Signal layer.

Inner Layer 2 (Layer 3): Ground plane (GND). Acts as the core ground plane.

Inner Layer 3 (Layer 4): Ground plane (GND). The second ground plane (may also be designed as a ground/power hybrid layer, but prioritise ground filling).

Inner Layer 4 (Layer 5): Power plane (VCC).

Bottom Layer (Layer 6): Signal layer.

Advantages:

The presence of two complete and adjacent ground planes (L3 and L4) significantly enhances ground plane continuity and provides very low ground impedance.

The two adjacent ground planes form a low-impedance ‘ground cavity’, offering excellent shielding and EMI performance.

Particularly suitable for designs requiring multiple ground plane divisions (such as the separation of analogue and digital grounds) or those with extremely high ground noise requirements.

The dielectric layer between L3 and L4 is relatively thin, resulting in a stronger capacitive effect and effective high-frequency decoupling.

The power plane (L5) also benefits from the presence of a good ground plane (L4) as a reference.

Disadvantages:

This configuration sacrifices routing resources on two signal layers (L2 and L6), leaving fewer signal layers available for routing compared to Scheme 1.

Signals on Layer 2 must traverse to Layer 3 to obtain a reference plane (unless Layer 1 or Layer 3 is used as the reference), which may increase the difficulty of impedance control or cause crosstalk issues, thereby increasing design complexity.

Key advantages of a 6 layer PCB

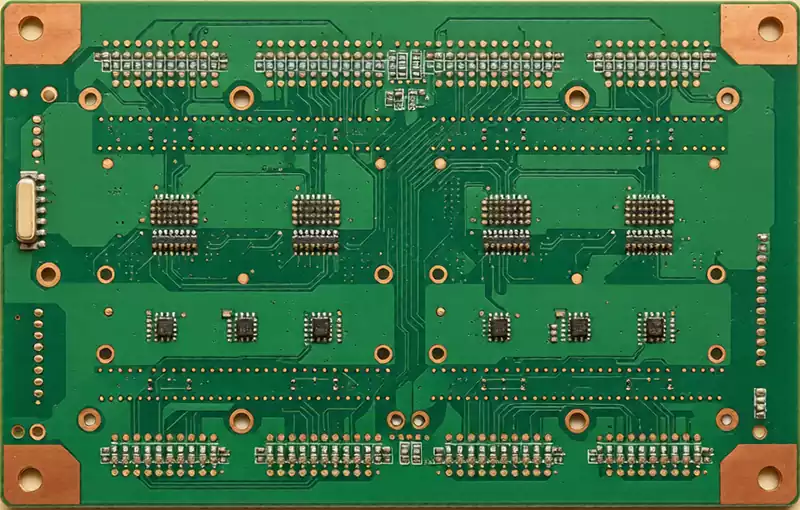

Superior signal integrity: This is the core advantage of a 6 layer pcb. It provides a complete reference plane. A typical stack-up structure (e.g., signal layer – ground layer – signal layer – power layer – signal layer – ground layer) offers a clear, low-impedance return path for high-speed signals, significantly reducing signal reflections and crosstalk. This forms the cornerstone of high-speed digital circuits (such as processors and high-speed interfaces) and RF circuits.

Strong Interference Resistance: The inner power and ground planes form a natural electromagnetic shielding cage, which not only prevents internal high-speed signals from radiating noise externally but also defends against external electromagnetic interference, making it easier for products to pass stringent EMC certification.

Higher Routing Density and Flexibility: With two additional layers of routing space, engineers no longer need to struggle with densely packed traces. Dedicated layers for power and ground networks simplify routing, allowing signal traces to flow more freely and smoothly, thereby enabling the design of smaller, more compact products.

Improved power distribution: Dedicated power layers provide stable voltage and extremely low impedance, effectively reducing power supply noise and supplying chips with a clean, efficient ‘energy drink’, ensuring stable system operation.

Common Challenges in 6 layer PCB Layout Design

Even when stack-up configurations have been standardised, layout design errors remain the primary cause of rework during mass production or equipment malfunctions.

Crosstalk between internal signal layers: Excessively long parallel runs of high-speed traces and a lack of isolation design can easily lead to signal distortion. This is typically caused by excessive compression of the board area and overly dense routing.

Unreasonable ground plane segmentation: Fragmented ground planes or compartmentalised power supply areas can sever current return paths, amplifying EMI risks, and are extremely difficult to rectify at a later stage.

Improper via design: Cross-layer vias can cause impedance discontinuities, directly affecting the quality of high-speed signal transmission.

Practical Design Guidelines for Mass Production

Drawing on extensive experience collaborating with PCB manufacturers, adhering to the following design principles can help avoid most structural defects:

Finalise the layer stack-up scheme before commencing routing. Making ad-hoc changes to the layer structure mid-design will affect impedance parameters and ground plane planning, thereby delaying project progress.

High-speed traces and sensitive analogue circuits should be routed as close as possible to a continuous ground plane to utilise ground plane shielding and reduce interference.

Strictly limit unnecessary inter-layer vias. Each via introduces parasitic capacitance and inductance, which compromise signal stability. Internal traces should be routed within a single layer wherever possible to minimise layer changes.

Coordinate promptly with the manufacturer to conduct a Design for Manufacturability (DFM) review. Many narrow-pitch, thin-copper designs that pass simulation tests are unsuitable for large-scale mass production; allowing reasonable process margins can significantly reduce the defect rate in batch production of 6 layer pcbs.

Mainstream Application Scenarios

Thanks to their balanced performance and cost advantages, 6 layer PCBs have become widely adopted across a range of moderately complex electronic products:

Industrial Automation: Controllers, sensor gateways and precision instruments utilise the 6 layer PCB’s interference resistance to withstand complex industrial electromagnetic environments.

Consumer Electronics: Mid-range smart wearables, router motherboards and whole-home smart control modules commonly employ a six-layer structure.

In-vehicle low-speed assistance systems: Body control modules and parking assistance equipment utilise 6 layer pcbs to ensure adequate heat dissipation and anti-interference capabilities.

6 layer pcbs perfectly bridge the market gap between low-cost four-layer boards and high-cost multi-layer boards, making them suitable for the vast majority of mid-range hardware projects.

Key Considerations for Cost and Mass Production Processing

Compared to four-layer boards, six-layer structures require more insulating materials and lamination processes, resulting in a moderate increase in overall procurement costs; however, they offer far better value for money than eight-layer or higher multilayer boards.

Production lead times vary depending on the stack-up configuration: the economical standard stack-up process is mature and highly efficient in mass production, resulting in shorter delivery cycles; signal-optimised versions require higher standards for interlayer alignment and quality inspection, leading to slightly longer production cycles.

For R&D projects requiring a balance between performance, lead times and budget, confirming the stack-up specifications with the PCB supplier at an early stage is key to avoiding cost overruns and delays in mass production.

With its balanced performance and cost, the 6 layer PCB is the ideal choice for mid-range hardware design. By selecting the appropriate stack-up scheme and avoiding common design pitfalls, an optimal balance can be achieved between signal integrity, manufacturability and project budget.